| •        |                                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------|

| 2        |                                                                                                                    |

| 3        |                                                                                                                    |

| 4        | SFP-DD MSA                                                                                                         |

| 5        |                                                                                                                    |

| 6        | SFP-DD/SFP-DD112 Hardware Specification                                                                            |

| 7        |                                                                                                                    |

| 8        | for                                                                                                                |

| 9        |                                                                                                                    |

| 10       | SFP DOUBLE DENSITY PLUGGABLE TRANSCEIVER                                                                           |

| 11       |                                                                                                                    |

| 12       | Revision 5.2                                                                                                       |

| 13<br>14 | October 27, 2022                                                                                                   |

| 14       | October 27, 2023                                                                                                   |

| 16       |                                                                                                                    |

| 17       | Abstract: This specification defines: the electrical and optical connectors, electrical signals and power supplies |

| 18       | mechanical and thermal requirements of the pluggable Double Density SFP-DD module, and Double Density              |

| 19       | SFP-DD112 connector and cage system. This document provides a common specification for systems                     |

| 20       | manufacturers, system integrators, and suppliers of modules.                                                       |

| 21       |                                                                                                                    |

| 22       |                                                                                                                    |

| 23       |                                                                                                                    |

| 24       |                                                                                                                    |

## 25 POINTS OF CONTACT:

Ali Ghiasi (Technical Editor) Ghiasi Quantum 19947 Lindenbrook Lane Cupertino, CA 95014 ali at ghiasiquantum dot com Scott Sommers (Chair) Molex 2222 Wellington Court Lisle, IL 60532-1682 scott.sommers at molex dot com

#### 26 27

1

## 28 Website:

- 29 <u>www.sfp-dd.com</u>

- 30

- 31 Limitation on use of Information:

- This specification is provided "**AS IS**" with **NO WARRANTIES** whatsoever and therefore the provision of this specification does not include any warranty of merchantability, noninfringement, fitness for a particular purpose, or any other warranty otherwise arising out of any proposal, specification or sample. The authors further disclaim all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

- 39 Permissions:

- 40 You are authorized to download, reproduce and distribute this document. All other rights are reserved. The

- 41 provision of this document should not be construed as the granting of any right to practice, make, use or

- 42 otherwise develop products that are based on the document. Any and all IP rights related to this document

- and the designs disclosed within, except for the rights expressly mentioned above, are reserved by the

- 44 respective owners of those IP rights.

- 45 46

#### The following are Promoter member companies of the SFP-DD MSA.

| Alibaba Group     | Hewlett Packard Enterprise | Lumentum        |

|-------------------|----------------------------|-----------------|

| Broadcom          | Huawei                     | Molex           |

| Cisco             | Intel                      | TE Connectivity |

| Coherent          | Juniper Networks           |                 |

| Dell Technologies | Nvidia                     |                 |

#### 2 3 4

1

#### The following are Contributor member companies of the SFP-DD MSA.

| Accelink                        | Genesis Connected Solutions | Nokia                |

|---------------------------------|-----------------------------|----------------------|

| Amphenol                        | Hisense Broadband           | Senko                |

| AOI                             | Infinera                    | Source Photonics     |

| Eoptolink                       | InnoLight                   | US Conec             |

| Foxconn Interconnect Technology | Analog Devices              | Yamaichi Electronics |

| Fourte International            | MultiLane                   | ZTE                  |

5 6 7

## Change History:

| Revision | Date               | Changes                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | September 14 2017  | Initial public release.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.0      | September 17, 2018 | Added Type 2 module. Changed IntL pin to reserved, Changed TxFault to TxFault/Int<br>Updated drawings to include new key. Added test conditions for insertion removal forces.                                                                                                                                                                                                                                                |

| 3.0      | April 10 2019      | Added 5 W power class. Added SN, MDC connectors. Deleted requirement that host shall not change the state of LPMode when module is present.                                                                                                                                                                                                                                                                                  |

| 4.0      | Withdrawn          |                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.1      | August 10, 2020    | Added ResetL, IntL, ePPS, Fault signals.<br>Added timing tables for low speeds signals, soft control and status.<br>Chapter 7-Management Interface is now part of Chapter 4-Electrical<br>Specification. Port mapping, optical connectors, and module color coding<br>moved out of Mechanical and Board Definition Chapter-5 and into a new<br>Chapter-5. Appendix A- Normative Connector Performance Requirements<br>added. |

| 4.2      | August 17, 2020    | Added dual functionality IntL/TXFaultDD signal definition for SFP-DD.                                                                                                                                                                                                                                                                                                                                                        |

| 5.0      | October 1, 2021    | Added chapter 5 Electrical Specifications for SFP112, added chapter 8<br>Mechanical specification of SFP-DD112, added chapter 9 Mechanical<br>Specification of SFP112. Added ePPS/Clock signals definition for SFP-<br>DD/SFP-DD112.                                                                                                                                                                                         |

| 5.1      | March 11, 2022     | Defined a new improved power supply test method 4.10, squelch level reduced to 50 mV for 112G operation 4.8.2. TWI bus timing removed from chapter 4 as identical timing diagram already included in CMIS.                                                                                                                                                                                                                   |

| 5.2      | October 27, 2023   | SFP-DD112 improved module paddle card 7.3 added option for double or triple split in the pre-wipe signal pads. SFP112 chapters are removed as they are now documented as SFP2 in the SFF-TA-1031 [28].                                                                                                                                                                                                                       |

8 9

## Foreword

10 The development work on this specification was done by the SFP-DD MSA, an industry group. The

11 membership of the committee since its formation in May 2017 has included a mix of companies which are 12 leaders across the industry.

13

The members of the SFP-DD MSA would like to acknowledge the contributions of Edmund Poh. He was an

excellent engineer; his technical skills and collaborative attitude will be missed.

| 2        |                                                                                                                       |    |

|----------|-----------------------------------------------------------------------------------------------------------------------|----|

| 3        | 1. Scope                                                                                                              |    |

| 4        | 1.1 Overview of SFP-DD/SFP-DD112 Specifications                                                                       |    |

|          | · ·                                                                                                                   |    |

| 5        | 2. References                                                                                                         |    |

| 6        | 2.1 Industry Documents                                                                                                |    |

| 7<br>8   | <ul> <li>2.2 SFF Specifications:</li> <li>2.3 Sources</li> </ul>                                                      |    |

|          |                                                                                                                       |    |

| 9        | 3. Introduction                                                                                                       | 9  |

| 10       | 3.1 Objectives                                                                                                        |    |

| 11       | 3.2 SFP-DD/SFP-DD112 System Overview                                                                                  |    |

| 12       | 3.3 Applications                                                                                                      | 11 |

| 13       | 4. Electrical Specification and Management Interface Timing for SFP-DD/SFP-DD112                                      | 12 |

| 14       | 4.1 General Requirements                                                                                              |    |

| 15       | 4.2 Electrical Connector                                                                                              |    |

| 16       | 4.3 Overview of the Low Speed Electrical Hardware Signals                                                             |    |

| 17       | 4.3.1 TxDisable, TxDisableDD                                                                                          |    |

| 18<br>19 | <ul><li>4.3.2 RxLOS, RxLOSDD</li><li>4.3.3 Speed1, Speed2, Speed1DD, Speed2DD</li></ul>                               |    |

| 20       | 4.3.4 TxFault                                                                                                         |    |

| 21       | 4.3.5 IntL/TxFaultDD                                                                                                  |    |

| 22       | 4.3.6 Mod_ABS                                                                                                         |    |

| 23       | 4.3.7 LPMode                                                                                                          |    |

| 24       | 4.3.8 ResetL                                                                                                          |    |

| 25<br>26 | <ul> <li>4.3.9 ePPS/Clock PTP Reference Clock (Optional)</li> <li>4.3.10 TWI Signals SCL, SDA</li> </ul>              |    |

| 27       | 4.4 Example SFP-DD/SFP-DD112 Host Board Schematics                                                                    |    |

| 28       | 4.5 Low Speed Electrical Specification                                                                                |    |

| 29       | 4.5.1 TWI Logic Levels and Bus Loading                                                                                |    |

| 30       | 4.6 Management Interface and Timing                                                                                   |    |

| 31<br>32 | 4.6.1 Management Timing Specification                                                                                 |    |

| 33       | 4.8 High Speed Electrical Specifications                                                                              |    |

| 34       | 4.8.1 RD0+, RD0-, RD1+, RD1                                                                                           |    |

| 35       | 4.8.2 TD0+, TD0-, TD1+, TD1                                                                                           |    |

| 36       | 4.9 Rate Select Hardware Control                                                                                      |    |

| 37       | 4.10 Power Requirements                                                                                               |    |

| 38<br>39 | <ul><li>4.10.1 Power Classes and Maximum Power Consumption</li><li>4.10.2 Host Board Power Supply Filtering</li></ul> |    |

| 40       | 4.10.3 Module Power Supply Specification                                                                              |    |

| 41       | 4.10.4 Host Board Power Supply Noise Output                                                                           |    |

| 42       | 4.10.5 Module Power Supply Noise Output                                                                               |    |

| 43       | 4.10.6 Module Power Supply Noise Tolerance                                                                            |    |

| 44       | 4.11 ESD                                                                                                              |    |

| 45       | 5. Optical Port Mapping and Optical Interfaces                                                                        |    |

| 46       | 5.1 Electrical data input/output to optical port mapping                                                              |    |

| 47       | 5.2 Optical Interfaces                                                                                                |    |

| 48       | 5.2.1 MPO Optical Cable connections                                                                                   |    |

| 49<br>50 | <ul><li>5.2.2 Duplex LC Optical Cable connection</li><li>5.2.3 SN Optical Cable connections</li></ul>                 |    |

| 50       | 5.2.3 SN Optical Cable connections                                                                                    |    |

| 52       | 5.3 Module Color Coding and Labeling                                                                                  |    |

| 53       | 6. SFP-DD Mechanical and Board Definition                                                                             |    |

|          |                                                                                                                       |    |

|          |                                                                                                                       |    |

**TABLE OF CONTENTS**

| 1                    | 6.1     | Introduction to SFP-DD and SFP-DD112                        | 40 |

|----------------------|---------|-------------------------------------------------------------|----|

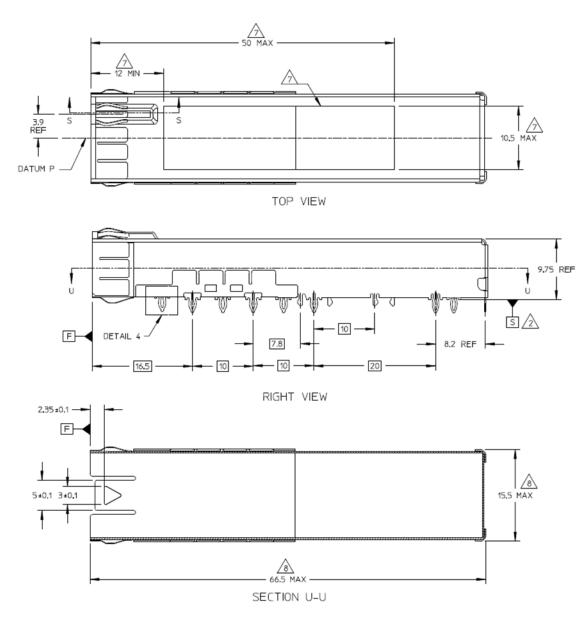

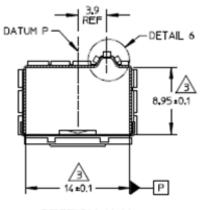

| 2                    | 6.2     | SFP-DD/SFP-DD112 Datums, Dimensions and Component Alignment |    |

| 3                    | 6.3     | SFP-DD Cage, Connector, Module Alignment                    |    |

| 4                    | 6.4     | SFP-DD/SFP-DD112 Module Mechanical Dimensions               |    |

| 5                    | 6.5     | SFP-DD/SFP-DD112 Module Flatness and Roughness              | 48 |

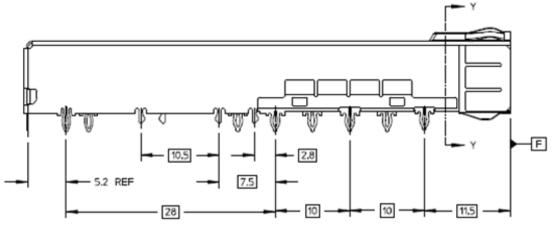

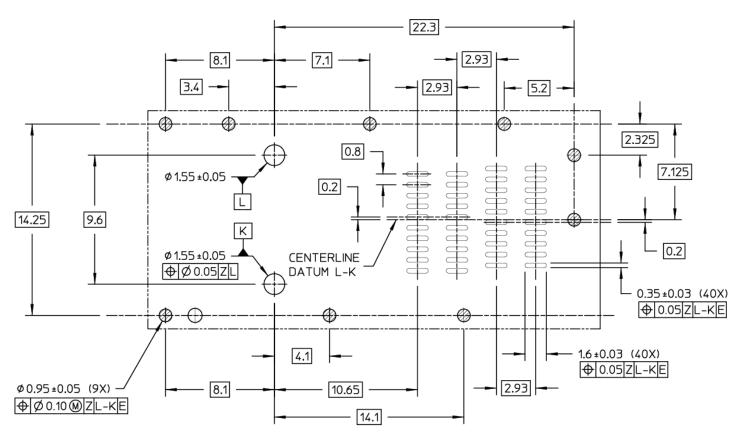

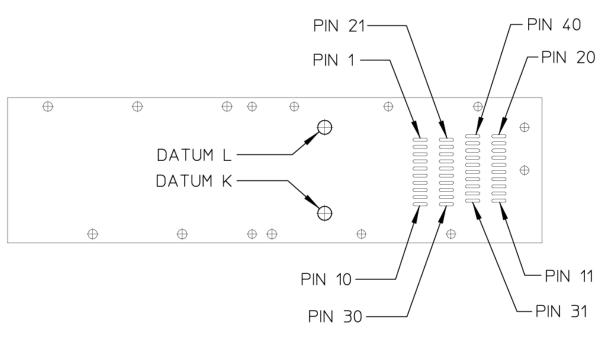

| 6                    | 6.6     | SFP-DD Module paddle card dimensions                        |    |

| 7                    | 6.7     | SFP-DD/SFP-DD112 Module Extraction and Retention Forces     | 51 |

| 8                    | 6.8     | Press fit Cage Mechanical                                   | 51 |

| 9                    | 6.9     | SMT Electrical Connector Mechanical                         | 57 |

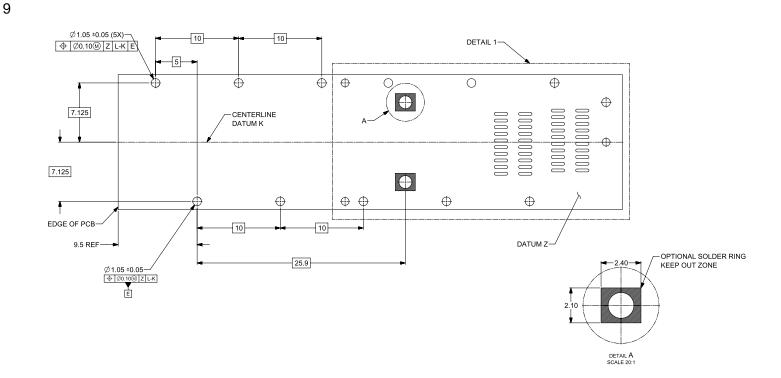

| 10                   | 6.9     | .1 SMT connector and cage host PCB layout                   | 60 |

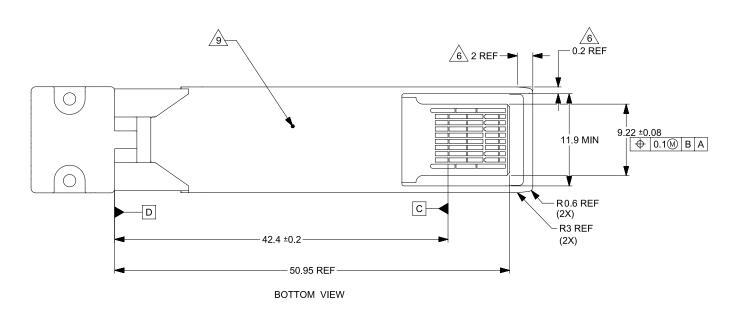

| 11                   | 7. SFI  | P-DD112 Mechanical and Board Definition                     | 62 |

| 12                   | 7.1     | Introduction                                                | 62 |

| 13                   | 7.2     | SFP-DD112 module mechanical dimensions                      |    |

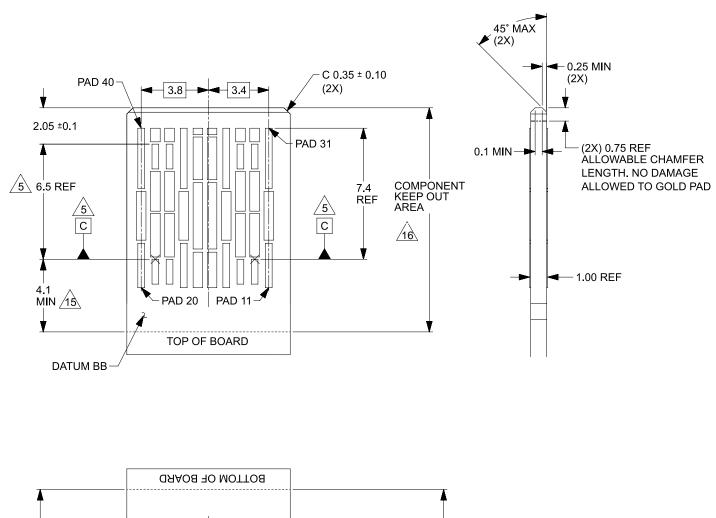

| 14                   | 7.3     | SFP-DD112 Improved Module paddle card dimensions            | 63 |

| 15                   | 7.4     | Press fit Cage Mechanical                                   |    |

| 16                   | 7.5     | SMT Electrical Connector Mechanical                         |    |

| 17                   | 7.5     | .1 SMT connector and cage host PCB layout                   | 69 |

| 18                   | 8. Env  | vironmental and Thermal                                     | 71 |

| 19                   | 8.1     | Thermal Requirements                                        | 71 |

| 20                   | Appendi | x A Normative Module and Connector Performance Requirements | 72 |

| 21<br>22<br>23<br>24 | A.1     | Performance Tables                                          | 72 |

| 1  | List of Tables                                                                                  |    |

|----|-------------------------------------------------------------------------------------------------|----|

| 2  |                                                                                                 |    |

| 3  | Table 1- Pad Function Definition                                                                | 15 |

| 4  | Table 2- ePPS/Clock Advertising Capabilities                                                    | 18 |

| 5  | Table 3- ePPS or Clock Modes                                                                    | 18 |

| 6  | Table 4- ePPS or Clock Frequency                                                                |    |

| 7  | Table 5- Low Speed Control and Sense Signals                                                    |    |

| 8  | Table 6- Management Interface timing parameters                                                 | 25 |

| 9  | Table 7- Timing for SFP-DD/SFP-DD112 soft control and status functions                          |    |

| 10 | Table 8- I/O Timing for Squelch & Disable                                                       | 27 |

| 11 | Table 9- TX Squelch Levels                                                                      |    |

| 12 | Table 10- Rate Select Hardware Control                                                          | 29 |

| 13 | Table 11- Power Classification                                                                  |    |

| 14 | Table 12- Power Supply specifications, Instantaneous, sustained and steady state current limits | 31 |

| 15 | Table 13- Power Supply Output Noise and Tolerance Specifications                                |    |

| 16 | Table 14- Electrical data input to Optical Port Mapping                                         | 36 |

| 17 | Table 15- Datum Description                                                                     | 42 |

| 18 | Table 16- Module flatness specifications                                                        | 48 |

| 19 | Table 17- Temperature Range Class of operation                                                  | 71 |

| 20 | Table 18- Form Factor Performance Requirements                                                  | 72 |

| 21 | Table 19- EIA-364-1000 Test Details                                                             | 73 |

| 22 | Table 20- Additional Test Procedures                                                            |    |

| 23 |                                                                                                 |    |

# List of Figures

| 19       Figure 17: MPO-12 Single Row optical patch cord and module receptacle.       37         20       Figure 18: Duplex LC optical patchcord and module nose height.       38         21       Figure 19: LC connector excursion above module nose height.       38         22       Figure 20: Minimum vertical port pitch.       38         23       Figure 21: SN optical connector plug and two-port module receptacle.       38         24       Figure 22: MDC optical connector plug and two-port module receptacle.       39         25       Figure 23: Press fit cage.       40         26       Figure 24: SFP-DD and SFP-DD112 Modules.       41         27       Figure 25: Cage, Connector alignment.       43         28       Figure 27: Detailed dimensions of module.       47         39       Figure 28: Module paddle card dimensions.       49         31       Figure 30: Press Fit 1x1 Cage.       50         32       Figure 31: Press Fit 1x1 Cage.       51         33       Figure 32: Press Fit Cage Detail       55         34       Figure 32: Press Fit Cage Detail       55         35       Figure 31: A n bezel opening       56         36       Figure 33: 1 x n bezel opening       56         35       Figure 35: 1x1 Connector Design and Host PCB Pin Numbers                                                                                                                                                   | 1        | List of Figures                                                                  |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------|----|

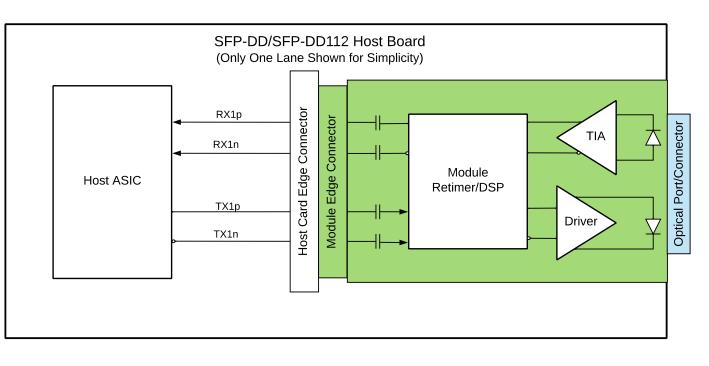

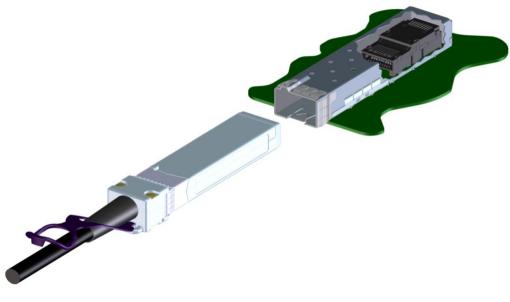

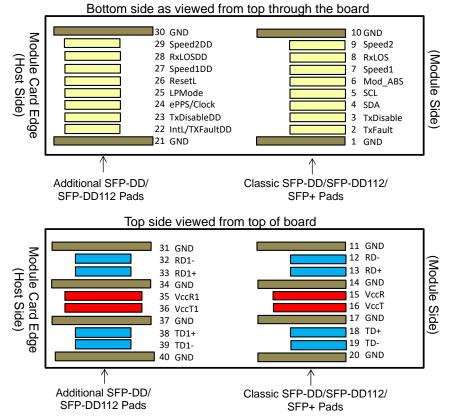

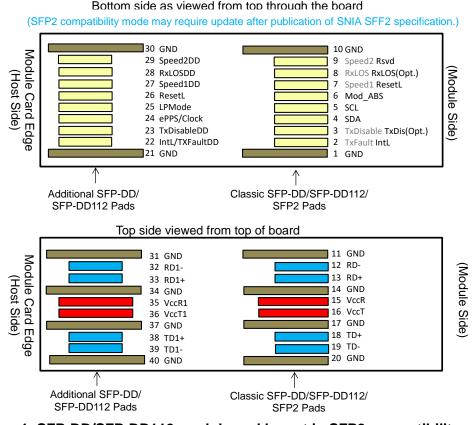

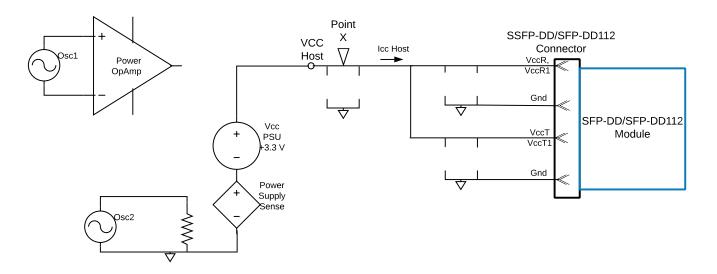

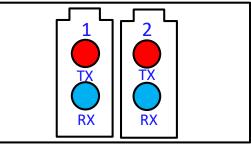

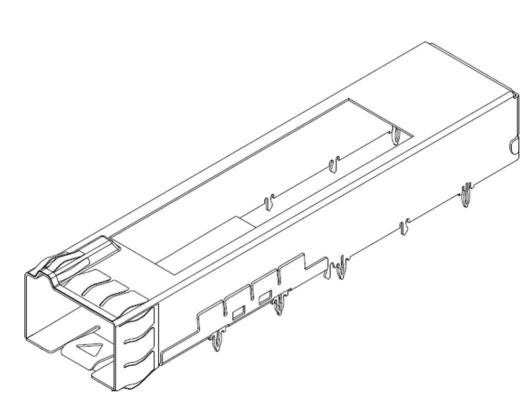

| 4       Figure 2: SFP-DD/SFP-DD112 Cage, Connector and Module       11         Figure 3: SFP-DD/SFP-DD112 module pad layout in SFP2 compatibility mode.       14         6       Figure 6: Stample SFP-DD/SFP-DD112 Host Board Schematic for Optical Modules.       19         7       Figure 6: Example SFP-DD/SFP-DD112 Host Board Schematic for optical Modules.       19         9       Figure 6: SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times.       23         11       Figure 8: SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times.       23         12       Figure 10: Recommended Host Board Power Supply Filtering.       30         13       Figure 11: Instantaneous and sustained peak currents for Icc Host (see Table 12).       32         14       Figure 12: Host Noise Output Measurement.       33         15       Figure 13: Module High Frequency Noise Tolerance.       35         16       Figure 16: Optical Media Dependent Interface port assignments.       36         17       Figure 18: Loc connector optical patchcord and module receptacle.       37         27       Figure 19: Module Low Frequency Noise Tolerance.       38         18       Figure 18: Loc connector optical patch cord and module receptacle.       37         20       Figure 16: Optical Media Dependent Interface port assignments.       38                                              |          | Figure 1: Application Reference Model                                            | 11 |

| 5       Figure 3: SFP-DD/SFP-DD112 module pad layout overlaid with SFP+ pads.       14         7       Figure 4: SFP-DD/SFP-DD112 Host Board Schematic for Optical Modules       19         8       Figure 6: Example SFP-DD/SFP-DD112 Host Board Schematic for active copper cables       20         9       Figure 7: Example SFP-DD/SFP-DD112 Host Board Schematic for active copper cables       21         10       Figure 8: SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times       23         12       Figure 9: SFP-DD/SFP-DD112 wo Wire Interface Timing       30         13       Figure 10: Recommended Host Board Power Supply Filtering       30         13       Figure 11: Instantaneous and sustained peak currents for Icc Host (see Table 12)       32         14       Figure 13: Module Noise Output Measurement       32         15       Figure 14: Module Holf Prequency Noise Tolerance       35         16       Optical Media Dependent Interface opt assignments       36         17       Figure 18: Duplex LC optical patch cord and module receptacle       37         19       L2 connector excursion above module nose height       38         19       L2 connector plug and two-port module receptacle       38         21       Str P-DD 112 Modules       44         21       Str publex LC optical connector plug and two-port modul                                                           |          |                                                                                  |    |

| 6       Figure 4: SFP-DD/SFP-DD112 module pad layout in SFP2 compatibility mode.       14         7       Figure 6: Example SFP-DD/SFP-DD112 Host Board Schematic for Optical Modules.       19         8       Figure 6: Example SFP-DD/SFP-DD112 Host Board Schematic for active copper cables.       20         9       Figure 8: SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times.       23         11       Figure 8: SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times.       23         12       Figure 10: Recommended Host Board Power Supply Filtering.       30         13       Figure 11: Instantaneous and sustained peak currents for loc Host (see Table 12)       32         14       Figure 12: Host Noise Output Measurement       33         15       Figure 13: Module how Frequency Noise Tolerance.       35         15       Figure 16: Optical Media Dependent Interface port assignments.       36         19       Figure 17: MPO-12 Single Row optical patch cord and module receptacle.       37         21       Figure 18: Duplex LC optical patch cord and module receptacle.       37         22       Module Mulle Active patch and wo-port module receptacle.       38         23       Figure 21: SN optical connector plug and two-port module receptacle.       38         24       Figure 22: Sape, Connector alignment.       43 </td <td></td> <td></td> <td></td> |          |                                                                                  |    |

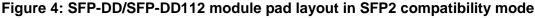

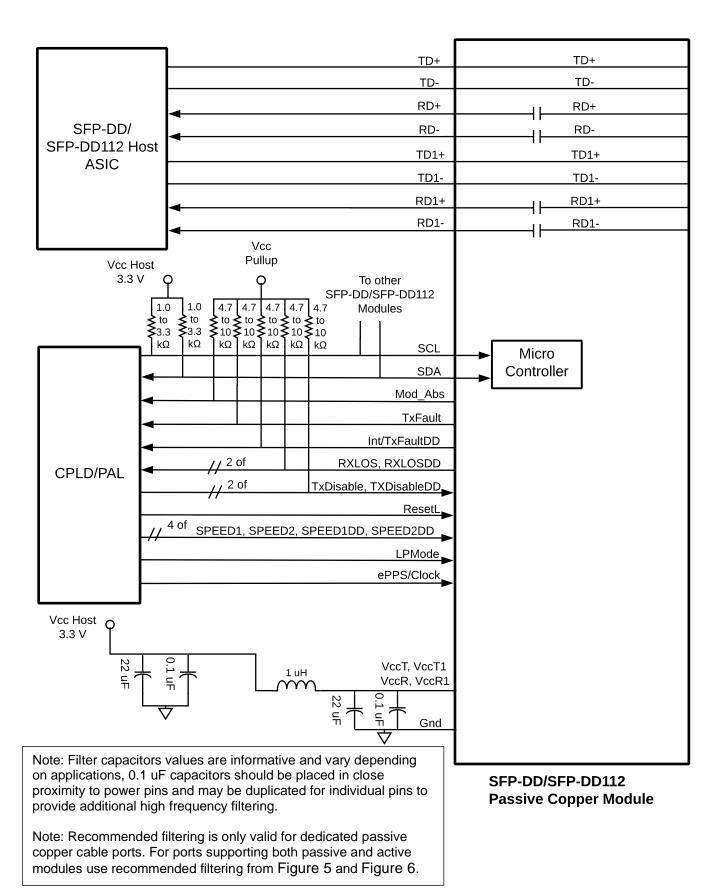

| 7       Figure 5: Example SFP-DD/SFP-DD112 Host Board Schematic for Optical Modules       19         8       Figure 6: Example SFP-DD/SFP-DD112 Host Board Schematic for passive copper cables       20         9       Figure 8: SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times       23         10       Figure 9: SFP-DD/SFP-DD112 Wow Wire Interface Timing       24         12       Figure 10: Recommended Host Board OPower Supply Filtering.       30         31       Figure 11: Instantaneous and sustained peak currents for Icc Host (see Table 12)       32         32       Figure 13: Module Noise Output Measurement       33         33       Figure 14: Module High Frequency Noise Tolerance       35         34       Figure 15: Module Low Frequency Noise Tolerance       36         35       Figure 16: Optical Media Dependent Interface port assignments       36         36       Figure 17: MPO-12 Single Row optical patch cord and module receptacle       37         37       Figure 18: Duplex LC optical connector plug and two-port module receptacle       38         38       Figure 21: SN optical connector plug and two-port module receptacle       38         39       Figure 22: MDC optical connector plug and two-port module receptacle       38         30       Figure 23: Press Fit cage       40         31       Figur                                                           |          |                                                                                  |    |

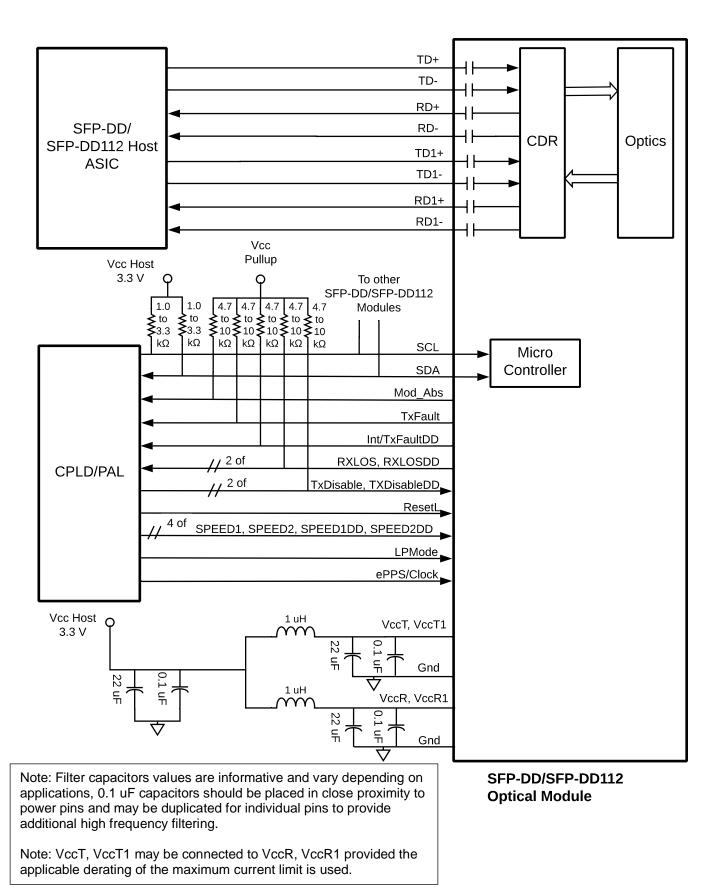

| 8       Figure 6: Example SFP-DD/SFP-DD112 Host Board Schematic for active copper cables       20         9       Figure 7: Example SFP-DD/SFP-DD112 Host Board Schematic for passive copper cables       21         11       Figure 8: SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times       23         11       Figure 10: Recommended Host Board Power Supply Filtering       30         13       Figure 11: Instantaneous and sustained peak currents for Icc Host (see Table 12)       32         14       Figure 12: Host Noise Output Measurement       33         15       Figure 13: Module Noise Output Measurement       33         16       Figure 15: Module Low Frequency Noise Tolerance       35         17       Figure 16: Optical Media Dependent Interface port assignments       36         18       Figure 19: LC connector excursion above module nose height       38         29       Figure 21: SN optical connector plug and two-port module receptacle       38         21       Figure 22: MDC optical connector plug and two-port module receptacle       39         21       Figure 24: STP-DD and STP-DD112 Modules       40         22       MDC optical donnector plug and two-port module receptacle       39         23       Figure 23: Press fit cage       41         24       Figure 24: STP-DD and STP-DD112 Modules                                                                      |          |                                                                                  |    |

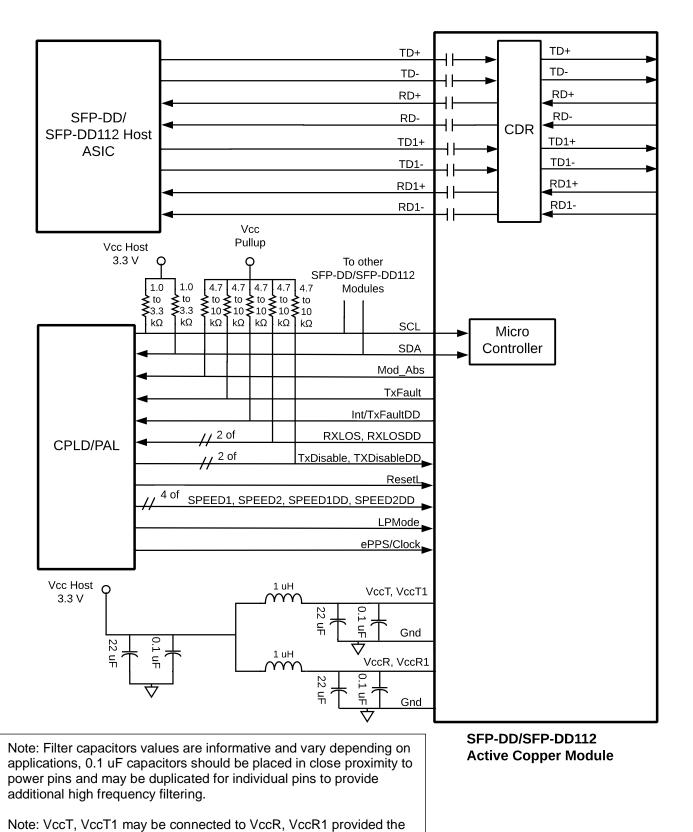

| 9       Figure 7: Example SFP-DD1/SFP-DD112 Host Board Schematic for passive copper cables       21         10       Figure 8: SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times       23         11       Figure 9: SFP-DD1/SFP-DD112 Two Wire Interface Timing       24         12       Figure 10: Recommended Host Board Power Supply Filtering       30         13       Figure 11: Instantenous and sustained peak currents for Icc Host (see Table 12)       32         14       Figure 13: Module Noise Output Measurement       33         15       Figure 14: Module High Frequency Noise Tolerance       35         16       Figure 15: Module Low Frequency Noise Tolerance       36         17       Figure 16: Optical Media Dependent Interface port assignments       36         18       Figure 17: MPO-12 Single Row optical patch cord and module receptacle       37         19       Figure 18: Duplex LC optical patch cord and module receptacle       38         21       Figure 20: Minimum vertical port pitch.       38         23       Figure 21: SN optical connector plug and two-port module receptacle       39         24       Figure 22: MDC optical connector plug and two-port module receptacle       39         25       Figure 23: Cage. Connector alignment.       43         26       Figure 24: SFP-DD12       Module                                                                    |          |                                                                                  |    |

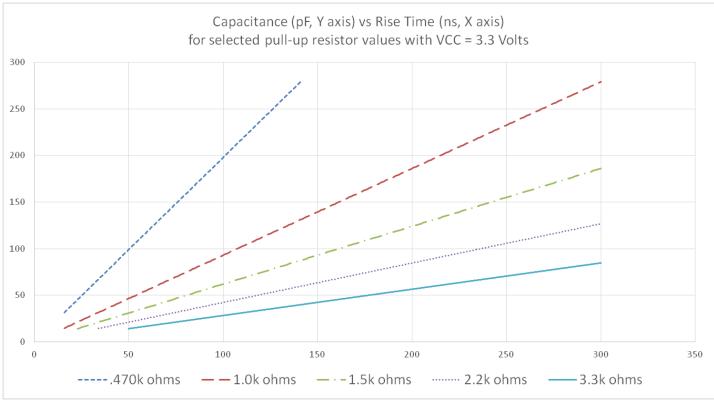

| 10       Figure 8: SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times.       23         11       Figure 10: Recommended Host Board Power Supply Filtering.       30         13       Figure 11: Instantaneous and sustained peak currents for Icc Host (see Table 12).       32         14       Figure 11: Instantaneous and sustained peak currents for Icc Host (see Table 12).       32         15       Figure 13: Module Noise Output Measurement.       32         16       Figure 14: Module High Frequency Noise Tolerance.       35         17       Figure 15: Module Low Frequency Noise Tolerance.       36         18       Figure 16: Optical Media Dependent Interface port assignments.       36         19       Figure 18: Duplex LC optical patchcord and module receptacle.       37         20       Figure 18: Duplex LC optical patchcord and module receptacle.       38         21       Figure 21: SN optical connector plug and two-port module receptacle.       38         23       Figure 22: MDC optical connector plug and two-port module receptacle.       39         24       Figure 24: SFP-DD and SFP-DD112 Modules.       41         25       Figure 24: SFP-DD and SFP-DD112 Modules.       41         26       Figure 25: Cage, Connector alignment.       43         27       Figure 26: Type 1 and Type 2 Modules. <t< td=""><td></td><td></td><td></td></t<>                              |          |                                                                                  |    |

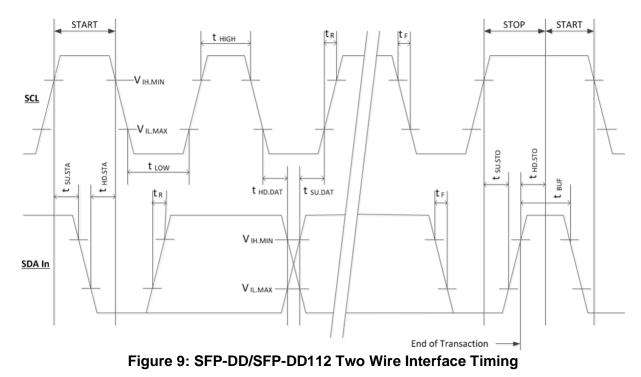

| 11       Figure 9: SFP-DD/SFP-DD112 Two Wire Interface Timing       24         12       Figure 10: Recommended Host Board Power Supply Filtering       30         30       Figure 11: Instantaneous and sustained peak currents for Icc Host (see Table 12)       32         31       Figure 12: Host Noise Output Measurement       33         32       Figure 13: Module Noise Cutput Measurement       33         33       Figure 14: Module High Frequency Noise Tolerance       35         33       Figure 16: Optical Media Dependent Interface port assignments       36         30       Figure 16: Optical Media Dependent Interface port assignments       36         31       Figure 16: Optical Media Dependent Interface port assignments       36         32       Figure 19: LC connector excursion above module receptacle       37         33       Figure 21: SN optical connector plug and two-port module receptacle       38         34       Figure 22: MDC optical connector plug and two-port module receptacle       39         35       Figure 24: SFP-DD and SFP-DD112 Modules       41         36       Figure 24: SFP-DD and SFP-DD112 Modules       41         37       Figure 25: Cage, Connector alignment       43         36       Figure 31: No beta od mensions       49         37       Figure 32: Type 1 and Ty                                                                                                       | 10       |                                                                                  |    |

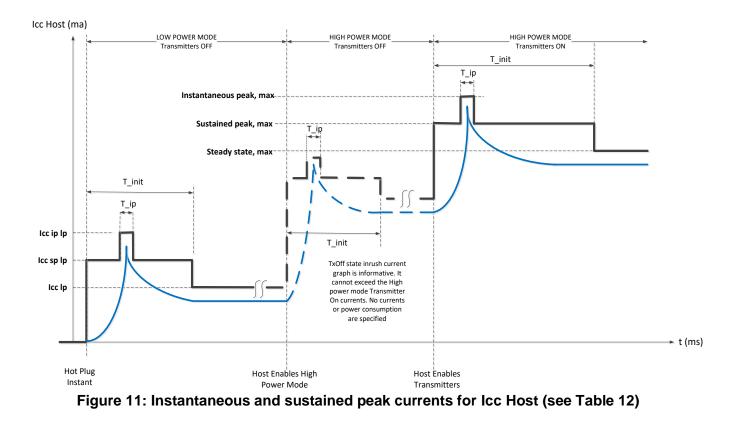

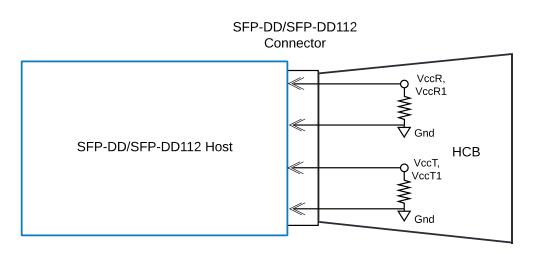

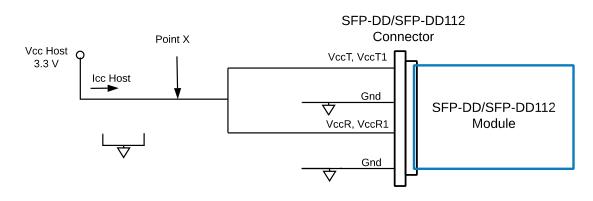

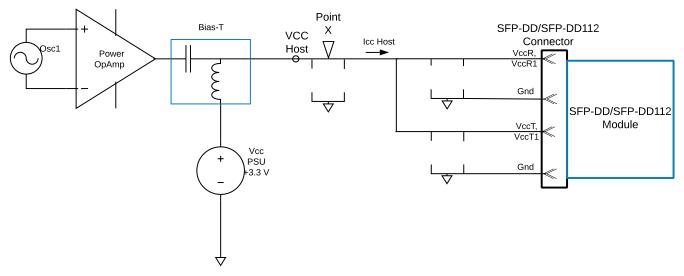

| 13       Figure 11: Instantaneous and sustained peak currents for Icc Host (see Table 12)       32         14       Figure 12: Host Noise Output Measurement       33         15       Figure 13: Module Noise Output Measurement       33         16       Figure 14: Module High Frequency Noise Tolerance       35         17       Figure 16: Optical Media Dependent Interface port assignments       36         19       Figure 17: MPO-12 Single Row optical patch cord and module receptacle       37         20       Figure 18: Duplex LC optical Patchcord and module receptacle       37         21       Figure 20: Minimum vertical port pitch.       38         22       Figure 21: SN optical connector plug and two-port module receptacle       39         23       Figure 22: MDC optical connector plug and two-port module receptacle       39         24       Figure 22: MDC optical connector plug and two-port module receptacle       39         25       Figure 26: Cage, Connector alignment.       43         26       Figure 27: Detailed dimensions of module       44         27       Figure 28: Module paddle card dimensions       49         36       Figure 30: Press Fit 1x1 Cage       50         37       Figure 31: Press Fit 1x1 Cage       51         38       Figure 32: Press Fit 1x1 Cage <td< td=""><td>11</td><td></td><td></td></td<>                                                                       | 11       |                                                                                  |    |

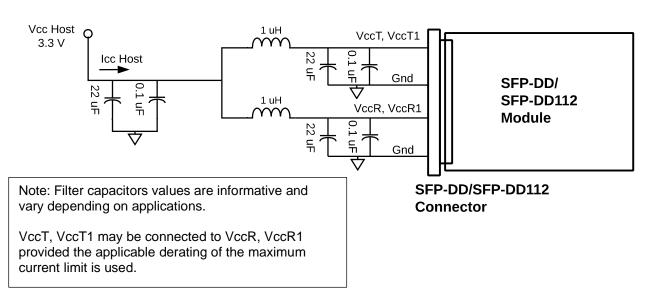

| 14       Figure 12: Host Noise Output Measurement       32         15       Figure 13: Module Noise Output Measurement       33         16       Figure 14: Module High Frequency Noise Tolerance       35         17       Figure 16: Optical Media Dependent Interface port assignments       36         18       Figure 16: Optical Media Dependent Interface port assignments       36         17       Figure 17: MPO-12 Single Row optical patch cord and module receptacle       37         20       Figure 18: Duplex LC optical patchcord and module receptacle       37         21       Figure 20: Minimum vertical port pitch       38         23       Figure 21: SN optical connector plug and two-port module receptacle       38         23       Figure 22: MDC optical connector plug and two-port module receptacle       38         24       Figure 23: Press fit cage.       40         25       Figure 24: SFP-DD and SFP-DD112 Modules       41         26       Figure 25: Cage, Connector and mensions       43         27       Figure 26: Type 1 and Type 2 Modules       44         29       Figure 28: Module padd dimensions       50         31       Figure 29: Module pad dimensions       50         32       Figure 29: Module padd dimensions       50         34 <t< td=""><td>12</td><td>Figure 10: Recommended Host Board Power Supply Filtering</td><td> 30</td></t<>                                                | 12       | Figure 10: Recommended Host Board Power Supply Filtering                         | 30 |

| 15       Figure 13: Module Noise Output Measurement       33         16       Figure 14: Module High Frequency Noise Tolerance       35         17       Figure 15: Module Low Frequency Noise Tolerance       35         18       Figure 15: Module Low Frequency Noise Tolerance       36         19       Figure 15: Module Low Frequency Noise Tolerance       36         19       Figure 16: Dotical Media Dependent Interface port assignments       36         19       Figure 17: MPO-12 Single Row optical patch cord and module receptacle       37         21       Figure 18: Duplex LC optical and module receptacle       38         22       Figure 21: SN optical connector plug and two-port module receptacle       38         23       Figure 22: MDC optical connector plug and two-port module receptacle       39         24       Figure 23: Press fit cage       40         25       Figure 24: SFP-DD and SFP-DD112 Modules       41         26       Figure 27: Detailed dimensions of module       47         37       Figure 27: Detailed dimensions of module       47         38       Figure 28: Module pad dimensions       50         39       Figure 30: Press Fit 1x1 Cage       51         31       Figure 31: Press Fit 1x1 Cage Design       54         34       Fig                                                                                                                                                   | 13       | Figure 11: Instantaneous and sustained peak currents for Icc Host (see Table 12) |    |

| 16       Figure 14: Module High Frequency Noise Tolerance.       35         17       Figure 15: Module Low Frequency Noise Tolerance.       35         18       Figure 16: Optical Media Dependent Interface port assignments.       36         19       Figure 18: Duplex LC optical patch cord and module receptacle.       37         20       Figure 19: LC connector excursion above module nose height.       38         21       Figure 20: Minimum vertical port pitch.       38         22       Figure 21: SN optical connector plug and two-port module receptacle.       38         23       Figure 23: Press fit cage.       40         26       Figure 24: SFP-DD and SFP-DD112 Modules.       41         27       Figure 26: Type 1 and Type 2 Modules.       41         28       Figure 27: Detailed dimensions of module.       47         30       Figure 28: Module pad dimensions.       49         31       Figure 30: Press Fit 1x1 Cage       51         32       Figure 30: Press Fit 1x2 Cage Design.       50         33       Figure 31: N tozel opening       50         34       Figure 32: Press Fit 1x1 Cage       51         33       Figure 33: 1 x n bezel opening       56         34       Figure 33: 1 x n bezel opening       56                                                                                                                                                                                       | 14       | Figure 12: Host Noise Output Measurement                                         |    |

| 17       Figure 15: Module Low Frequency Noise Tolerance.       35         18       Figure 16: Optical Media Dependent Interface port assignments.       36         18       Figure 17: MPO-12 Single Row optical patch cord and module receptacle.       37         20       Figure 18: Duplex LC optical patchcord and module receptacle.       37         21       Figure 19: LC connector excursion above module nose height       38         23       Figure 20: Minimum vertical port pitch.       38         24       Figure 21: SN optical connector plug and two-port module receptacle       38         25       Figure 23: Press fit cage.       40         26       Figure 24: SFP-DD and SFP-DD112 Modules       41         27       Figure 26: Type 1 and Type 2 Modules       41         28       Figure 27: Detailed dimensions of module       42         29       Figure 30: Press Fit 1x1 Cage       50         21       Figure 31: Press Fit 1x1 Cage       51         26       Figure 31: Press Fit 1x1 Cage       51         27       Figure 31: Nr bazel opening       56         38       Figure 31: Xn Connector       57         39       Figure 31: Xn bazel opening       56         316       Figure 31: Xn bazel opening       56 <td< td=""><td>15</td><td>Figure 13: Module Noise Output Measurement</td><td> 33</td></td<>                                                                                                  | 15       | Figure 13: Module Noise Output Measurement                                       | 33 |

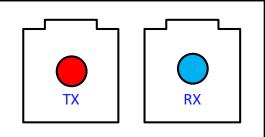

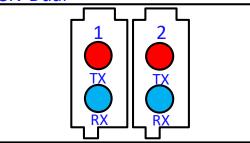

| 18       Figure 16: Optical Media Dependent Interface port assignments       36         19       Figure 17: MPO-12 Single Row optical patch cord and module receptacle.       37         20       Figure 18: Duplex LC optical patch cord and module receptacle.       37         21       Figure 19: LC connector excursion above module nose height       38         22       Figure 20: Minimum vertical port pitch.       38         23       Figure 21: SN optical connector plug and two-port module receptacle       39         24       Figure 22: MDC optical connector plug and two-port module receptacle       39         25       Figure 23: Press fit cage.       40         26       Figure 24: SPP-DD and SFP-DD112 Modules       41         27       Figure 26: Cape, Connector alignment.       43         28       Figure 27: Detailed dimensions of module       44         29       Figure 27: Detailed dimensions       40         21       Figure 28: Module pad dimensions       40         23       Figure 29: Module card dimensions       41         29       Figure 29: Module pad dimensions       40         21       Figure 29: Module pad limensions       50         22       Figure 30: Press Fit 1x1 Cage       51         313       Figure 30: Press Fit 1x1 Cage Desi                                                                                                                                                   | 16       | Figure 14: Module High Frequency Noise Tolerance                                 | 35 |

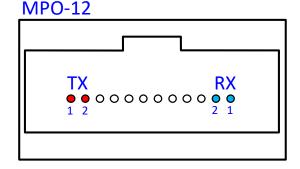

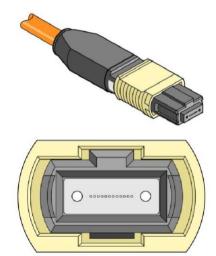

| 19       Figure 17: MPO-12 Single Row optical patch cord and module receptacle.       37         20       Figure 18: Duplex LC optical patchcord and module nose height.       38         21       Figure 19: LC connector excursion above module nose height.       38         23       Figure 20: Minimum vertical port pitch.       38         23       Figure 21: SN optical connector plug and two-port module receptacle.       38         24       Figure 22: MDC optical connector plug and two-port module receptacle.       39         25       Figure 23: Press fit cage.       40         26       Figure 24: SFP-DD and SFP-DD112 Modules.       41         27       Figure 25: Cage, Connector alignment.       43         28       Figure 26: Type 1 and Type 2 Modules       44         29       Figure 27: Detailed dimensions of module       47         31       Figure 30: Press Fit 1x1 Cage       50         32       Figure 30: Press Fit 1x1 Cage       51         33       Figure 32: Press Fit 1x1 Cage       51         34       Figure 31: N bezel opening       50         35       Figure 31: A n bezel opening       55         36       Figure 33: 1 x n bezel opening       55         35       Figure 33: 1 x n bezel opening       56                                                                                                                                                                                     | 17       |                                                                                  |    |

| 20       Figure 18: Duplex LC optical patchcord and module receptacle       37         21       Figure 19: LC connector excursion above module nose height       38         22       Figure 20: Minimum vertical port pitch       38         38       Figure 21: SN optical connector plug and two-port module receptacle       38         39       Figure 22: MDC optical connector plug and two-port module receptacle       39         20       Figure 23: Press fit cage.       40         21       Figure 24: SFP-DD and SFP-DD112 Modules       41         23       Figure 25: Cage, Connector alignment.       43         24       Figure 25: Cage, Connector alignment.       43         25       Figure 26: Type 1 and Type 2 Modules.       44         26       Figure 27: Detailed dimensions of module       47         27       Figure 28: Module pad dimensions       49         28       Figure 29: Module pad dimensions       50         29       Figure 31: Press Fit 1x1 Cage       51         31       Figure 31: Press Fit 1x1 Cage Design       54         39       Figure 33: 1x n bezel opening       56         30       Figure 33: 1x n bezel opening       57         33       Figure 35: 1x1 Connector Design and Host PCB Pin Numbers       59 <t< td=""><td>18</td><td></td><td></td></t<>                                                                                                                                     | 18       |                                                                                  |    |

| 21       Figure 19: LC connector excursion above module nose height       38         22       Figure 20: Minimum vertical port pitch       38         23       Figure 21: SN optical connector plug and two-port module receptacle       38         24       Figure 22: MDC optical connector plug and two-port module receptacle       39         25       Figure 23: Press fit cage       40         26       Figure 24: SFP-DD and SFP-DD112 Modules       41         27       Figure 25: Cage, Connector alignment       43         28       Figure 26: Type 1 and Type 2 Modules       44         29       Figure 27: Detailed dimensions of module       47         30       Figure 28: Module paddle card dimensions       49         31       Figure 30: Press Fit 1x1 Cage       50         32       Figure 31: Press Fit 1x1 Cage Design       54         34       Figure 32: Press Fit 1x1 Cage Design       56         35       Figure 33: 1 x n bezel opening       56         36       Figure 37: SFP-DD112 Module Bottom View Details       59         35       Figure 36: Host PCB Mechanical Layout       61         36       Figure 37: SFP-DD112 Module Bottom View Details       62         37       Figure 38: Improved module pad dimensions       62 <t< td=""><td></td><td></td><td></td></t<>                                                                                                                                       |          |                                                                                  |    |

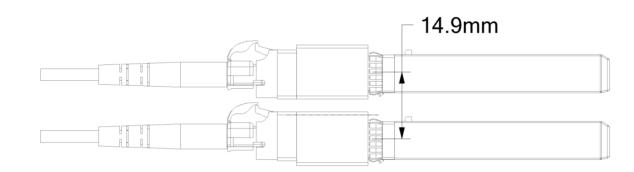

| 22       Figure 20: Minimum vertical port pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                                                                  |    |

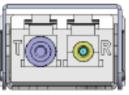

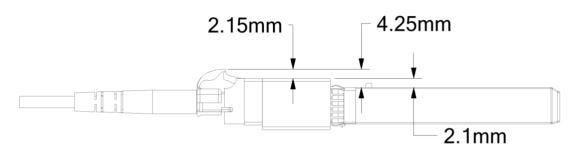

| 23Figure 21: SN optical connector plug and two-port module receptacle3824Figure 22: MDC optical connector plug and two-port module receptacle3925Figure 23: Press fit cage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                                                                  |    |

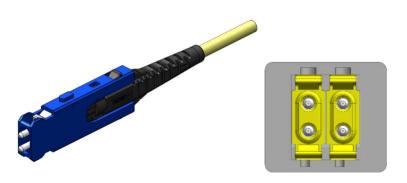

| 24Figure 22: MDC optical connector plug and two-port module receptacle3925Figure 23: Press fit cage4026Figure 24: SFP-DD and SFP-DD112 Modules4127Figure 25: Cage, Connector alignment.4328Figure 26: Type 1 and Type 2 Modules4429Figure 27: Detailed dimensions of module4730Figure 28: Module paddle card dimensions4931Figure 30: Press Fit 1x1 Cage5032Figure 31: Press Fit 1x1 Cage51331 x n bezel opening5635Figure 32: Press Fit Cage Detail5536Figure 33: 1 x n bezel opening5637Figure 33: 1 x n bezel opening5638Figure 37: SFP-DD112 Module Bottom View Details6139Figure 37: SFP-DD112 Module Bottom View Details6240Figure 39: Improved module paddle card dimensions6441Figure 39: Improved module padd imensions6542Figure 41: SMT connector6743Figure 41: SMT connector6444Figure 42: 1x1 Canee6645Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6546Figure 41: SMT connector6747Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6848Figure 42: 1x1 Connector6743Figure 42: 1x1 Connector6844Figure 42: 1x1 Connector6845Figure 43: Host PCB Mechanical Layout68 <td< td=""><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                             |          |                                                                                  |    |

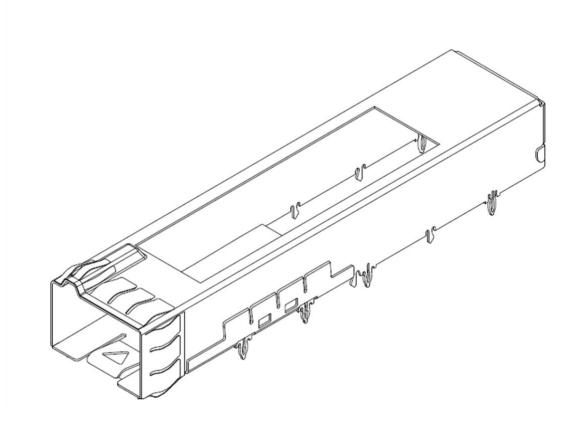

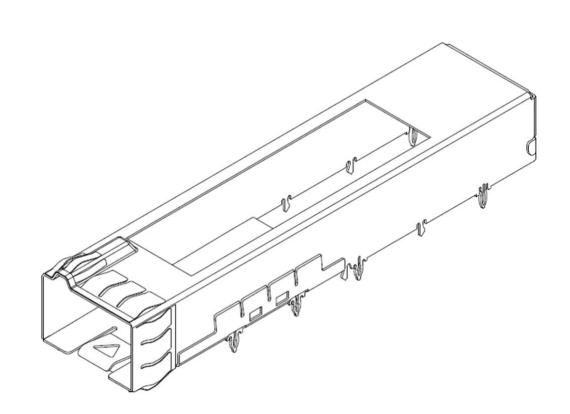

| 25Figure 23: Press fit cage4026Figure 24: SFP-DD and SFP-DD112 Modules4127Figure 25: Cage, Connector alignment.4328Figure 26: Type 1 and Type 2 Modules4429Figure 27: Detailed dimensions of module4730Figure 28: Module paddle card dimensions4931Figure 29: Module pad dimensions5032Figure 30: Press Fit 1x1 Cage5133Figure 32: Press Fit 1x1 Cage Design5444Figure 32: Press Fit Cage Detail5555Figure 33: 1 x n bezel opening5656Figure 35: 1x1 Connector Design and Host PCB Pin Numbers5938Figure 35: SFP-DD112 Module Bottom View Details6240Figure 39: Improved module paddle card dimensions6441Figure 39: Improved module pad dimensions6442Figure 41: SMT connector6743Figure 41: SMT connector6644Figure 42: Ix1 Connector Design and Host PCB Pin Numbers6245Figure 41: SMT connector6744Figure 42: Ix1 Connector6645Figure 41: SMT connector6746Figure 42: Ix1 Connector Design and Host PCB Pin Numbers6847Figure 42: Ix1 Connector6748Figure 43: Host PCB Mechanical Layout6749Figure 41: SMT connector6741Figure 42: Ix1 Connector Design and Host PCB Pin Numbers6845Figure 43: Host PCB Mechanical Layout                                                                                                                                                                                                                                                                                                                                |          |                                                                                  |    |

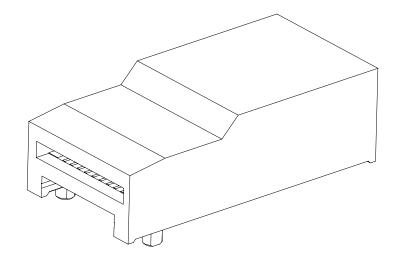

| 26Figure 24: SFP-DD and SFP-DD112 Modules4127Figure 25: Cage, Connector alignment4328Figure 26: Type 1 and Type 2 Modules4429Figure 27: Detailed dimensions of module4730Figure 28: Module paddle card dimensions4931Figure 29: Module pad dimensions5032Figure 30: Press Fit 1x1 Cage5133Figure 31: Press Fit 1x1 Cage Design5434Figure 32: Press Fit Cage Detail5535Figure 33: 1 x n bezel opening5636Figure 36: Host PCB Mechanical Layout6139Figure 37: SFP-DD112 Module Bottom View Details6240Figure 38: Improved module paddle card dimensions6441Figure 39: Improved module pad dimensions6442Figure 41: SMT connector6543Figure 41: SMT connector6544Figure 41: SMT connector6545Figure 41: SMT connector6546Figure 41: SMT connector6547Figure 41: SMT connector6548Figure 41: SMT connector6749Figure 41: SMT connector6741Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6843Figure 43: Host PCB Mechanical Layout6844Figure 43: Host PCB Mechanical Layout6745Figure 43: Host PCB Mechanical Layout6846Figure 43: Host PCB Mechanical Layout68 <tr <td="">Figure 43: Host PCB Mechan</tr>                                                                                                                                                                                                                                                                                                                                              |          |                                                                                  |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                                                                  |    |

| 27Figure 25: Cage, Connector alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                                                                                  |    |

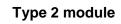

| 28Figure 26: Type 1 and Type 2 Modules4429Figure 27: Detailed dimensions of module4730Figure 28: Module paddle card dimensions4931Figure 29: Module pad dimensions5032Figure 30: Press Fit 1x1 Cage5133Figure 31: Press Fit 1x1 Cage Design5434Figure 32: Press Fit Cage Detail5535Figure 33: 1 x n bezel opening5636Figure 34: SMT connector5737Figure 35: 1x1 Connector Design and Host PCB Pin Numbers5938Figure 37: SFP-DD112 Module Bottom View Details6240Figure 38: Improved module pad dimensions6441Figure 39: Improved module pad dimensions6441Figure 41: SMT connector6744Figure 41: SMT connector6744Figure 41: SMT connector6745Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6845Figure 43: Host PCB Mechanical Layout.6845Figure 41: SMT connector67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                                                                  |    |

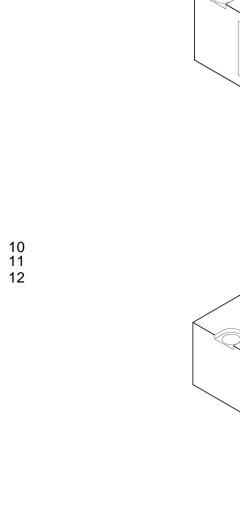

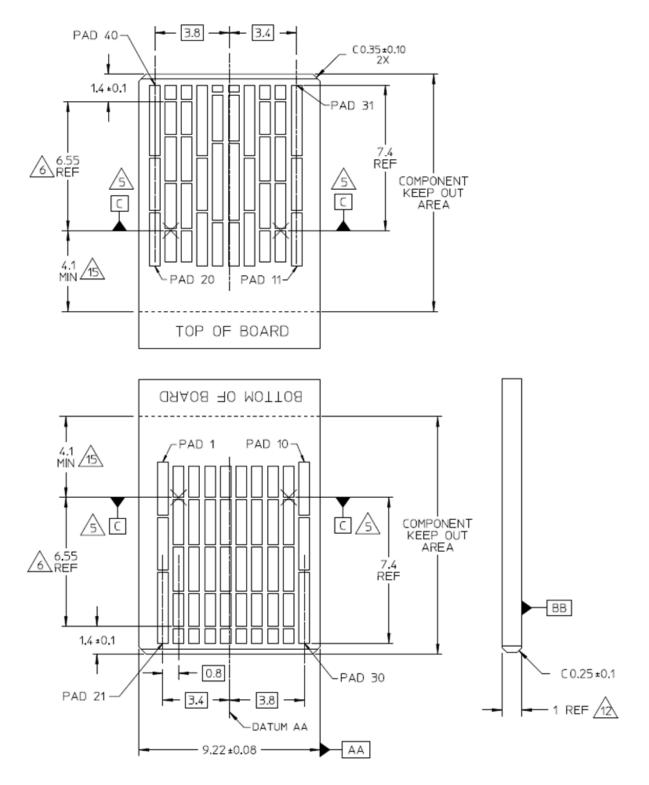

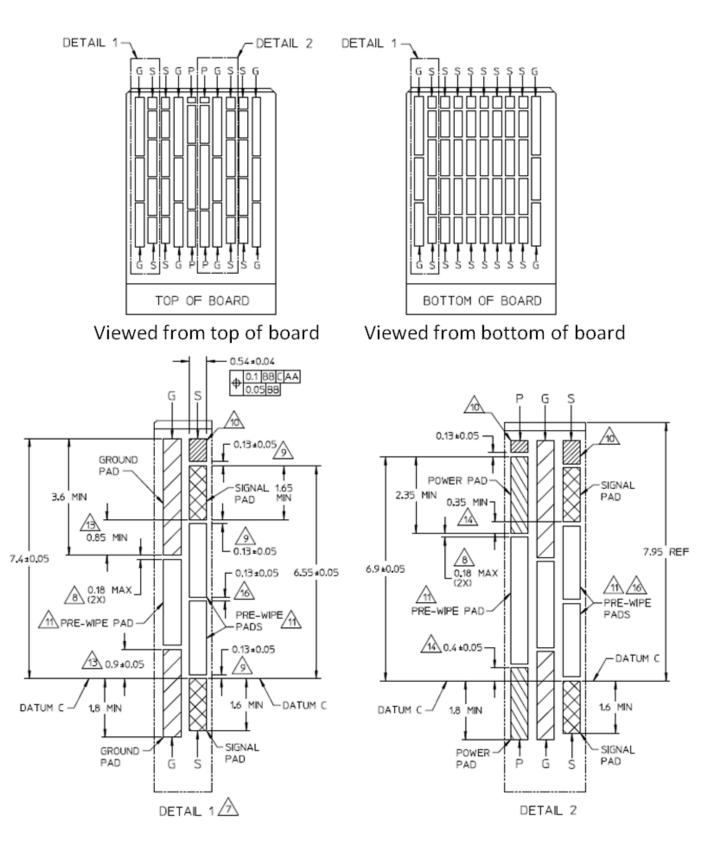

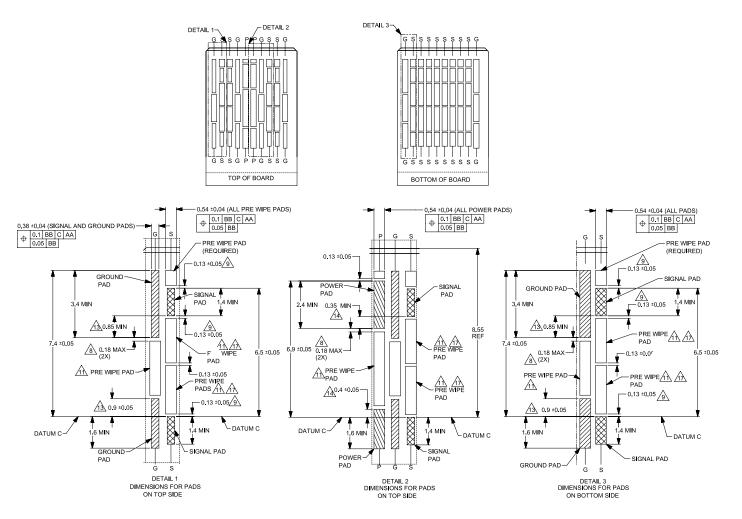

| 29Figure 27: Detailed dimensions of module4730Figure 28: Module paddle card dimensions4931Figure 29: Module pad dimensions5032Figure 30: Press Fit 1x1 Cage5133Figure 31: Press Fit 1x1 Cage Design5434Figure 32: Press Fit Cage Detail5535Figure 33: 1 x n bezel opening5636Figure 34: SMT connector5737Figure 35: 1x1 Connector Design and Host PCB Pin Numbers5938Figure 37: SFP-DD112 Module Bottom View Details6139Figure 38: Improved module paddle card dimensions6241Figure 39: Improved module pad dimensions6542Figure 40: Press Fit 1x1 Cage6643Figure 41: SMT connector6744Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6845Figure 43: Host PCB Mechanical Layout61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                                                                  |    |

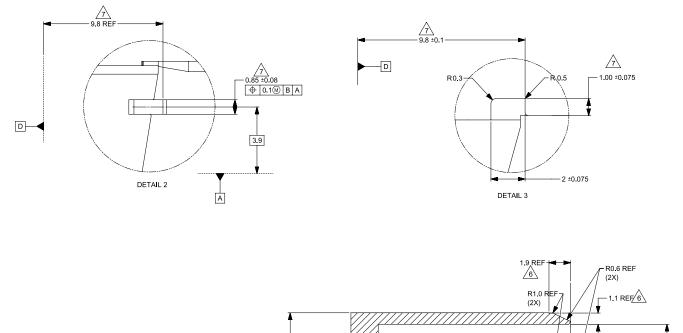

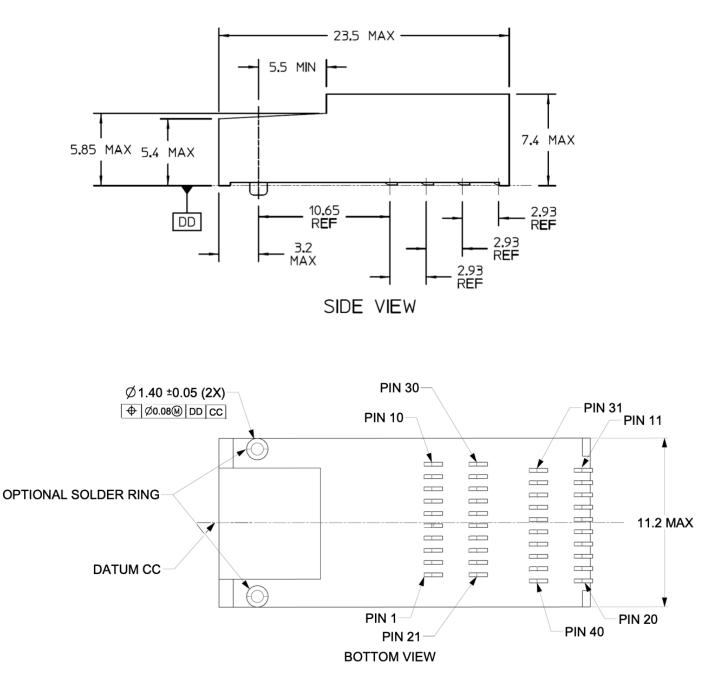

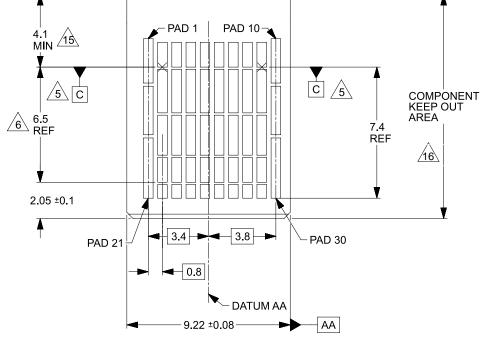

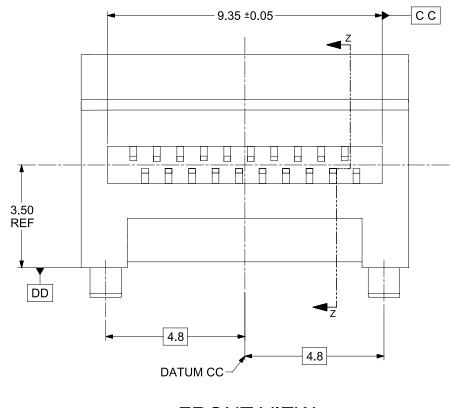

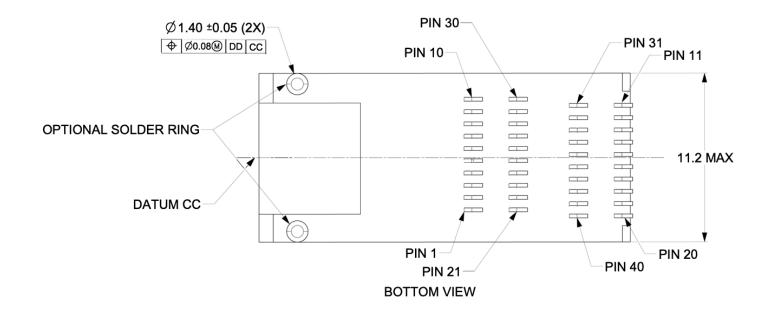

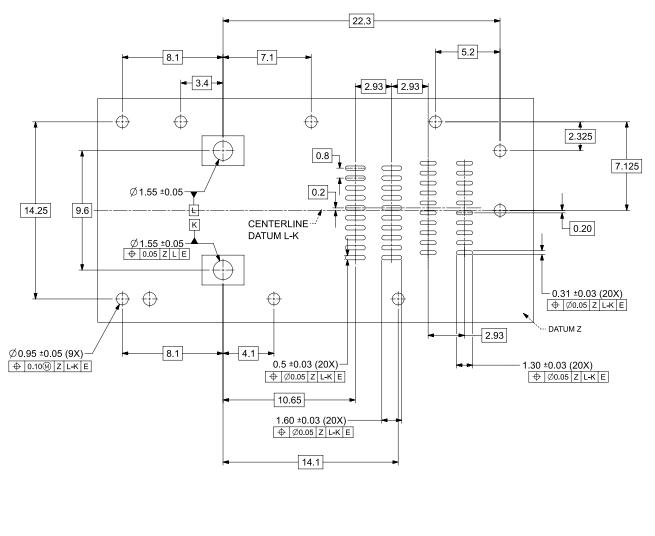

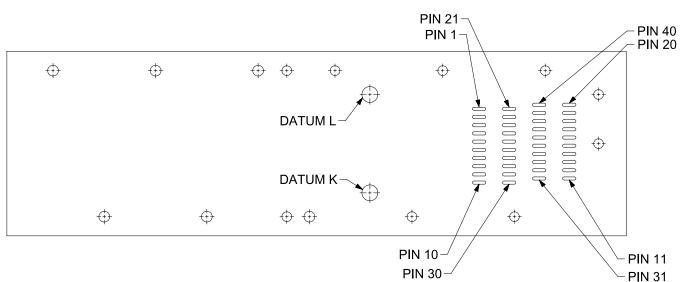

| 30Figure 28: Module paddle card dimensions4931Figure 29: Module pad dimensions5032Figure 30: Press Fit 1x1 Cage5133Figure 31: Press Fit 1x1 Cage Design5434Figure 32: Press Fit Cage Detail5535Figure 33: 1 x n bezel opening5636Figure 34: SMT connector5737Figure 36: Host PCB Mechanical Layout6139Figure 37: SFP-DD112 Module Bottom View Details6240Figure 38: Improved module paddle card dimensions6441Figure 39: Improved module paddle card dimensions6542Figure 40: Press Fit 1x1 Cage6643Figure 41: SMT connector6744Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6845Figure 43: Host PCB Mechanical Layout6845Figure 43: Host PCB Mechanical Layout70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                                                                                  |    |

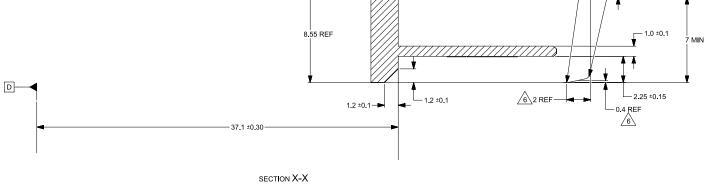

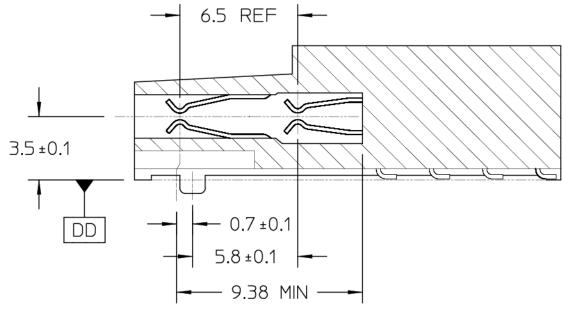

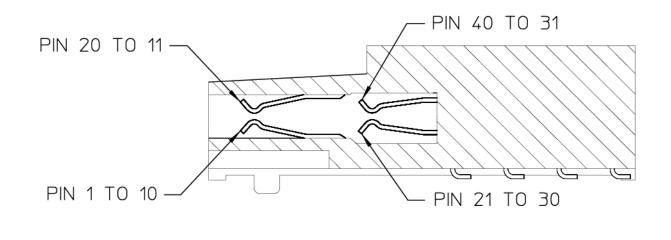

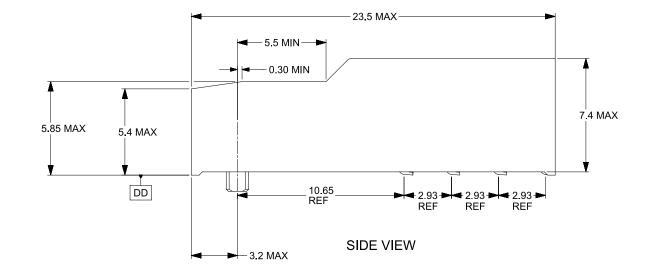

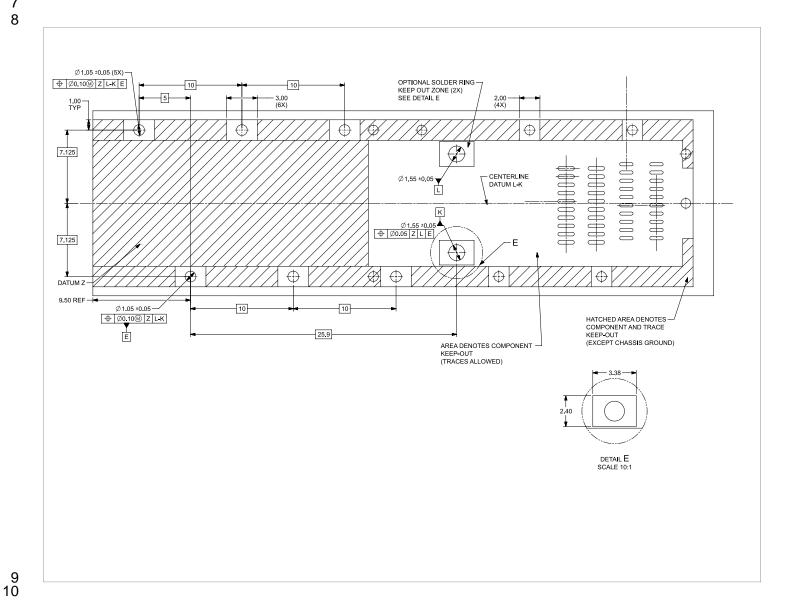

| 31Figure 29: Module pad dimensions5032Figure 30: Press Fit 1x1 Cage5133Figure 31: Press Fit 1x1 Cage Design5434Figure 32: Press Fit Cage Detail5535Figure 33: 1 x n bezel opening5636Figure 34: SMT connector5737Figure 35: 1x1 Connector Design and Host PCB Pin Numbers5938Figure 36: Host PCB Mechanical Layout6139Figure 37: SFP-DD112 Module Bottom View Details6240Figure 38: Improved module paddle card dimensions6441Figure 39: Improved module pad dimensions6542Figure 40: Press Fit 1x1 Cage6643Figure 41: SMT connector6744Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6845Figure 43: Host PCB Mechanical Layout70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                                                                  |    |

| 32Figure 30: Press Fit 1x1 Cage5133Figure 31: Press Fit 1x1 Cage Design5434Figure 32: Press Fit Cage Detail5535Figure 33: 1 x n bezel opening5636Figure 34: SMT connector5737Figure 35: 1x1 Connector Design and Host PCB Pin Numbers5938Figure 36: Host PCB Mechanical Layout6139Figure 37: SFP-DD112 Module Bottom View Details6240Figure 38: Improved module paddle card dimensions6441Figure 39: Improved module pad dimensions6542Figure 40: Press Fit 1x1 Cage6643Figure 41: SMT connector6744Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6845Figure 43: Host PCB Mechanical Layout70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                                                  |    |

| 33Figure 31: Press Fit 1x1 Cage Design.5434Figure 32: Press Fit Cage Detail5535Figure 33: 1 x n bezel opening5636Figure 34: SMT connector5737Figure 35: 1x1 Connector Design and Host PCB Pin Numbers5938Figure 36: Host PCB Mechanical Layout.6139Figure 37: SFP-DD112 Module Bottom View Details6240Figure 38: Improved module paddle card dimensions6441Figure 39: Improved module pad dimensions6542Figure 40: Press Fit 1x1 Cage6643Figure 41: SMT connector6744Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6845Figure 43: Host PCB Mechanical Layout.70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                                                                                  |    |

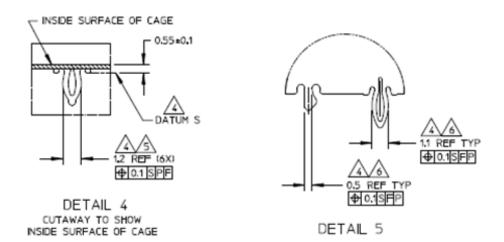

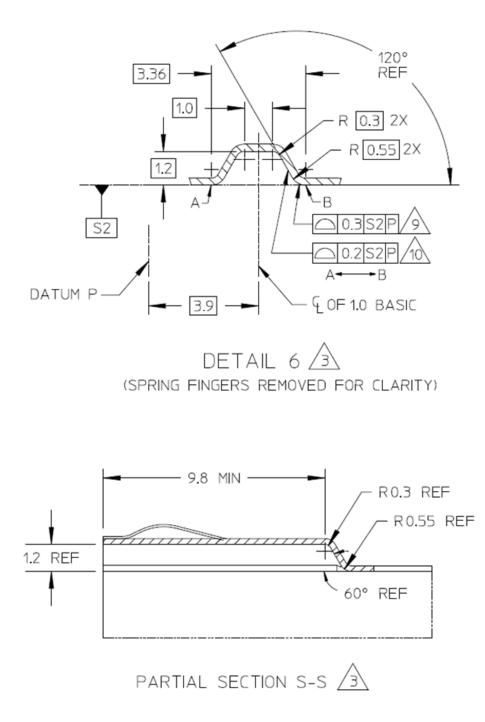

| 34Figure 32: Press Fit Cage Detail5535Figure 33: 1 x n bezel opening5636Figure 34: SMT connector5737Figure 35: 1x1 Connector Design and Host PCB Pin Numbers5938Figure 36: Host PCB Mechanical Layout6139Figure 37: SFP-DD112 Module Bottom View Details6240Figure 38: Improved module paddle card dimensions6441Figure 39: Improved module pad dimensions6542Figure 40: Press Fit 1x1 Cage6643Figure 41: SMT connector6744Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6845Figure 43: Host PCB Mechanical Layout70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                                                                  |    |

| 35Figure 33: 1 x n bezel opening5636Figure 34: SMT connector5737Figure 35: 1x1 Connector Design and Host PCB Pin Numbers5938Figure 36: Host PCB Mechanical Layout6139Figure 37: SFP-DD112 Module Bottom View Details6240Figure 38: Improved module paddle card dimensions6441Figure 39: Improved module pad dimensions6542Figure 40: Press Fit 1x1 Cage6643Figure 41: SMT connector6744Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6845Figure 43: Host PCB Mechanical Layout70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                                                                  |    |

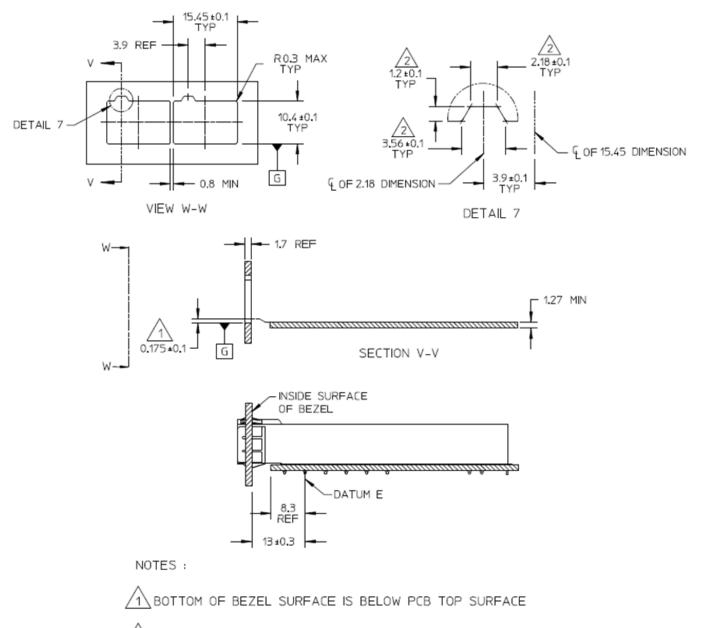

| 36Figure 34: SMT connector5737Figure 35: 1x1 Connector Design and Host PCB Pin Numbers5938Figure 36: Host PCB Mechanical Layout6139Figure 37: SFP-DD112 Module Bottom View Details6240Figure 38: Improved module paddle card dimensions6441Figure 39: Improved module pad dimensions6542Figure 40: Press Fit 1x1 Cage6643Figure 41: SMT connector6744Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6845Figure 43: Host PCB Mechanical Layout70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                                                                  |    |

| 37Figure 35: 1x1 Connector Design and Host PCB Pin Numbers5938Figure 36: Host PCB Mechanical Layout6139Figure 37: SFP-DD112 Module Bottom View Details6240Figure 38: Improved module paddle card dimensions6441Figure 39: Improved module pad dimensions6542Figure 40: Press Fit 1x1 Cage6643Figure 41: SMT connector6744Figure 42: 1x1 Connector Design and Host PCB Pin Numbers6845Figure 43: Host PCB Mechanical Layout70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                                                                                  |    |